BIBLIOTEKA GŁÓWNA

BIBLIOTEKA GŁÓWNA

# Stanisław J. Piestrak

Design of self-testing checkers for unidirectional error detecting codes

# Scientific Papers of the Institute of Technical Cybernetics of the Technical University of Wrocław

Monographs

No. 92

No. 24

1995

No. 92

Stanisław J. PIESTRAK

Design of self-testing checkers for unidirectional error detecting codes

| Prace Naukowe Instytutu Cybernetyki Techniczne<br>Politechniki Wrocławskiej | <b>92</b> |

|-----------------------------------------------------------------------------|-----------|

| Seria:<br>Monografie                                                        | 24        |

# Stanisław J. Piestrak

# Design of self-testing checkers for unidirectional error detecting codes

Monografie

Nr 24

1995

Concurrent error detection, error detecting codes,

fault-tolerant computing,

reliable digital circuit,

self-checking circuits, self-testing checker,

unidirectional error detecting codes

Stanisław J. Piestrak\*

# DESIGN OF SELF-TESTING CHECKERS FOR UNIDIRECTIONAL ERROR DETECTING CODES

Digital self-checking circuits wherein inputs, outputs, and internal states are encoded using error detecting codes (EDCs) allow for concurrent error detection of both permanent and temporary internal faults. For many years, it has been observed that many faults occurring in VLSI circuits, semiconductor memory systems, and optical disks cause unidirectional errors. In this monograph, a general approach for designing highly efficient hardware supporting the use of unidirectional error detecting codes (UEDCs) in fault-tolerant digital systems is presented. Included are the design methods of self-testing checkers (STCs) for nonsystematic UEDCs codes and both encoders and STCs for systematic UEDCs. The nonsystematic codes include the all-UED m-out-of-n codes and t-UED Borden codes. The systematic codes include: all-UED Berger and equivalent codes, t-UED codes, and burst-UED codes. The basic building blocks of all encoders and STCs presented here are parallel counters — which are entirely built of full- and half-adders, and multi-output threshold circuits — whose the most efficient version can be built using an identical simple cell. It is shown that the gate-level STCs proposed for all UEDCs considered here can be designed in a uniform way and that they can be made not only less complex and/or faster than existing designs but easily-testable as well. They also enjoy a highly regular structure composed of gates with low fan-in and fan-out, which makes them attractive for VLSI implementation.

<sup>\*</sup>Technical University of Wrocław, Institute of Engineering Cybernetics, ul. Wybrzeże Wyspiańskiego, 50-370 Wrocław

#### LIST OF ABBREVIATIONS

ALU - arithmetic-logic unit

AUEDC — all-unidirectional error detecting code

BUEDC — burst-unidirectional error detecting code

CD — code-disjoint

CED — concurrent error detection

CLA — carry lookahead adder

CPA — carry-propagate adder

CSA — carry-save adder

EAC — end-around-carry

ECC — error-correcting code EDC — error-detecting code

FA — full-adder FS — fault-secure FT — fault-tolerant

FTC — fault-tolerant computing

HA — half-adder IF — inverter-free

LSB — least significant bit

MLB code — maximal length Berger code

m/n code — m-out-of-n code (constant-weight code)

mod — modulo

MSB — most significant bit

OSUC — optimal systematic unordered code

PLA — programmable logic array

RAM — random access memory

ROM — read only memory

s/z — stuck-at-z SC — self-checking

SEC — single-error correcting

SFS — strongly fault-secure

SN — sorting network

ST — self-testing

STC — self-testing checker

TSC — totally self-checking

t-UEDC — t-unidirectional error detecting code

UEDC — unidirectional error detecting code

u-error — unidirectional error

VLSI — very large scale integration

#### LIST OF SYMBOLS

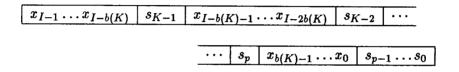

```

length of burst error

b(K)

maximum length of burst error detected by a code with

K check bits

(c1 cn)

two outputs of an STC

set of codewords

C_{2r}

2-rail code

Berger code with I information bits and K check bits

C_{(I,K)}

input code space of a circuit \mathbf{H} (C_{IN} \subset \mathbf{X})

C_{IN}

n-bit t-UED Borden code

C(n,t)

COUT

output code space of a circuit H (C_{OUT} \subset \mathbf{Z})

fault in a circuit H

f

F

set of likely faults in a circuit H

number of gates in a circuit ·

Ga(\cdot)

H

combinational circuit with n inputs

Ι

number of information bits

In(\cdot)

total number of gate inputs in a circuit ·

information part of a codeword X of a systematic code

J_X = (x_{I-1} \dots x_0)

number of check bits (K = n - I)

K

L(\cdot)

number of gate levels in a circuit ·

length of codeword

(n;q)

parallel counter with n inputs and q outputs

number of 0s (1s) in a binary vector

p_0(p_1)

P_X = (s_{K-1} \dots s_0)

check part of a codeword X of a systematic code

multiplicity of unidirectional errors detected by a code

\mathbf{T}(\cdot)

test for a circuit ·

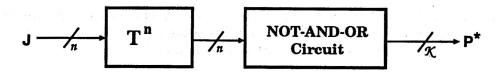

T^n

n-input n-output threshold circuit

n-variable threshold function with threshold i

T_{\cdot}^{n}

input vector of a circuit H; x_{n-1} (x_0) is MSB (LSB)

input space of a circuit \mathbf{H} (set of all 2^n input binary

n-tuples)

X^e

input non-codeword, i.e. X^e \in \{X \setminus C_{IN}\}

output space of H (set of all 2<sup>s</sup> output binary s-tuples)

\mathbf{Z}

```

#### 1. INTRODUCTION

The steady progress in microelectronics technology has made available VLSI components whose complexity is already counted in millions of transistors. However, despite significant improvement of reliability of all elementary components, reflected e.g. by their much lower failure rates, their large number required to build faster and more complex computer systems causes that the problem of fail-

ures cannot be ignored. Three types of behavior of a computer system which experiences component malfunctions can be distinguished: (i) it produces wrong data. (ii) it ceases to produce the intended data, or (iii) it does both at the same time. A spectrum of computer applications demanding both enhanced reliability and predictable behavior in case of failures has been growing continuously. The most notable examples are: (1) airline flight control (fly-by-wire), space applications, and real-time control of complex technological processes, that require continuous availability and absolute data integrity: (2) telephone switching networks, for which high availability is crucial; and (3) on-line transaction processing, such as airline reservation systems, banking, credit card verification, wherein data integrity is the overriding concern. In these critical applications, a computer outage during normal functioning may result in financial losses, massive inconvenience or loss of life. It is therefore desirable that the behavior of the computer system experiencing failures of its internal elements should be thoroughly thought over and implemented; e.g. the system should be provided with a special means to detect a failure, so that it can shut down all or part of the system, provide warnings or alarms, and possibly switch in back-up systems. In other words, the general objectives of a dependable computer system are: to prevent damage, to restore operation as quickly as possible, and to enhance required availability. However, modern computers are too sophisticated and failure mechanisms are too complex, so that any ad hoc approaches to design and implementation of a dependable system are infeasible. The only way is systematic implementation of proper dependability techniques at every level of computer architecture: from the lowest circuit-level to the highest system-level. It is therefore not surprising that dependable computing has evolved into a broad discipline that is related to very diverse areas of computer science and engineering, including VLSI logic design, computer organization and architecture, software engineering, and system design, which are supported by analytical and simulation techniques needed to perform validation, verification, and quantitative evaluation of dependability of computer systems.

# 1.1. Background and Motivation

Dependability is a global concept which subsumes the usual attributes of reliability (continuity of service), availability (readiness of usage), safety (avoidance of catastrophic consequences on the environment), and security (preservation of integrity and confidentiality) [85]. Fault avoidance and fault tolerance are two basic approaches to design of a dependable system. Fault avoidance is aimed at constructing a fault-free system, which can be achieved e.g. by using higher qual-

ity, thoroughly tested components. Fault tolerance is aimed at providing correct functional operation of the system even in the presence of faults whose occurrence is assumed inevitable. (Here we consider physical faults in hardware which accidentally occur within the system during its operation.) The major advantages of fault-tolerant (FT) techniques are a significant improvement in system availability and the feasibility of error-free computation, hence its potentially safer operation.

Dependability has been an important attribute since the early highly unreliable computers were constructed in the fifties [108], [109], [114], [7]. Despite continuous progress in manufacturing of digital components and assembling processes, the need for more and more dependable computation have continued until now, although the requirements towards dependability of digital systems changed in time, as the digital systems are expanding both in size and the number and variety of applications. This can be seen from a continuous flow of monographs on designing FT computers (given here in a chronological order of appearance): [210], [135], [181], [164], [171], [207], [78], [177], [159], [73], [165], [170], [189], [182].

The expectations towards dependability of many modern digital systems can be extremely high — the systems with availability even as high as 0.9999999 [182] and reliability of 10<sup>-9</sup> failures per hour over the 10 hour mission time [159] are considered. That even so high expectations towards dependability of digital systems are not exaggerated, the following crashes of large scale systems caused by hardware faults of control computers which have been reported in the nineties, are bitter reminders.

- 1. Jan. 15, 1990 the failure of the AT&T long-distance telephone network in the USA which lasted for nine hours [106], [183].

- 2. Feb. 1990 the crash of a "fly by wire" Airbus A320 in Bangalore, India [183].

- 3. Sept. 17, 1991 the seven and a half hour outage of the telecommunication network in the New York City [31].

- 4. June 26, 1993 the thirty hours long failure of the banking card network in France affecting 40% of 21 mln owners of banking cards in France during the whole weekend [88].

Many other incidents related to computer system failures were extensively reported in [105].

Fault tolerance of a digital system always requires introducing some redundancy into a system. Generally, the types of redundancy are classified as:

#### 1. Hardware redundancy;

- 2. Software redundancy;

- 3. Information redundancy; and

- 4. Time redundancy.

Although this classification is rather conventional as one type of redundancy (which is predominant) usually involves introducing some other types as well, it is still valuable as it indicates the type of redundancy which is prevalent. As an example, consider the information redundancy such as encoding of data with an error-detecting code (EDC) or an error-correcting code (ECC). Basically, it relies on introducing extra bits to any data unit, e.g. by encoding inputs and outputs of all circuits (and internal states—if a circuit is sequential) with EDCs or ECCs. However, it also involves hardware redundancy — in the form of encoders, decoders, extra datapath lines (to transmit) or memory bits (to store) these extra bits, as well as time redundancy — as the encoding and decoding of data may introduce some delay into a system.

Fault tolerance may be achieved by fault masking or fault detection followed by recovery. The former—more expensive—provides faster error correction while the latter requires less redundancy. The latter approach, which is of our concern, may involve duplication of a system (or its modules) with comparison and/or using EDCs, providing the circuitry with the possibility of on-line detection of internal faults, and appropriate design of recovery procedures. Since various classes of such circuits can be distinguished, we will use a generic term selfchecking (SC) circuits to denote all of them. Self-checking design offers concurrent error detection (CED), i.e. error detection performed in real-time continuously with the system functioning, of both permanent and temporary (both transient and intermittent) faults. This technique supports achieving fault tolerance of a digital system for temporary faults, provided that the sequence of events: error detection, rollback recovery, and operation retry is sucessfully performed. This approach is particularly welcome in many digital systems, when we recall that: (1) nowadays more than 90% of faults which occur during system operation are temporary [182] and they are difficult to detect (if at all) by applying periodic software diagnostic test procedures; and (2) the use of EDCs and implementing circuits as SC is relatively inexpensive. However, it must be pointed out that using EDCs can be economically justified if and only if it results in significantly less overhead than duplication with comparison, which always introduces more than 100% redundancy: one extra module and a comparator. Also, one should not overlook that duplication usually involves significantly less design effort to be implemented than other SC techniques. Another important problem with designing and implementing any FT digital system is the presence of a hardcore, which can be loosely defined as that part of the hardware that must be functioning correctly in order to initiate any diagnostic functions. The probability of hardcore failure can be reduced by using the following techniques: (i) minimizing the amount of hardware in the hardcore, e.g. by implementing circuits as SC or FT; (ii) implementing the hardcore using highly reliable components; and (iii) providing mechanism to facilitate periodic off-line testing the hardcore. A more extensive discussion of the hardcore problem can be found in [78].

The following recovery functions are performed within a FT system that uses fault detection and recovery, after a fault occurs. The first step in tolerating a fault is to detect an error produced as a result of it as soon as it is produced, before it propagates through the system. Once the fault is detected, the diagnosis whether the fault is permanent or temporary can be performed, e.g. through rollback and retry. In case of temporary fault, it is likely that the fault will disappear and the system may resume its operation without repair. Otherwise, it is assumed that a fault is permanent and its location up to a replaceable component is necessary for a possible reconfiguration of the system, which then may resume its operation, possibly with degraded performance.

The need for the use of coding techniques for providing digital systems with hardware means for on-line verification that the system operates correctly is very apparent from the wealth of applications of digital systems in which error-free computation is one of the key requirements. Once an internal fault occurs in the system, then it is desirable to detect it as quickly as possible. On one hand, the ever growing complexity of VLSI chips with decreasing size of internal devices makes modern digital systems more and more vulnerable to temporary faults. On the other hand, the decreasing price of hardware (relative to the cost of software development) justifies the use of hardware error handling techniques. The industrial experience of respected computer manufacturers such as Tandem Computers and Sun Microsystems proves that relying solely on the high reliability of VLSI integrated circuits and run-time checks to ensure data integrity of general-purpose microprocessor-based systems has become insufficient [61]. It is estimated that on average one out of 10000 personal computers per month experiences data corruption due to internal failures, which go undetected by commonly used traditional techniques of on-line error detection which rely on validity checks, parity control of the datapaths only, and ECCs of memory. It was explicitly pointed out that the density packed VLSI chips are already so susceptible to intermittent and transient faults, that the minimum of error protection, such as provided by an EDC, of most modules of a digital system becomes mandatory. Therefore, there is a strong motivation to support less expensive techniques of tolerating temporary faults that rely on control flow checking (for an excellent survey, see [190]) by significantly stronger methods such as SC design.

A number of different classes of error control codes have been constructed for

- 2. Software redundancy;

- 3. Information redundancy; and

- 4. Time redundancy.

Although this classification is rather conventional as one type of redundancy (which is predominant) usually involves introducing some other types as well, it is still valuable as it indicates the type of redundancy which is prevalent. As an example, consider the information redundancy such as encoding of data with an error-detecting code (EDC) or an error-correcting code (ECC). Basically, it relies on introducing extra bits to any data unit, e.g. by encoding inputs and outputs of all circuits (and internal states—if a circuit is sequential) with EDCs or ECCs. However, it also involves hardware redundancy — in the form of encoders, decoders, extra datapath lines (to transmit) or memory bits (to store) these extra bits, as well as time redundancy — as the encoding and decoding of data may introduce some delay into a system.

Fault tolerance may be achieved by fault masking or fault detection followed by recovery. The former—more expensive—provides faster error correction while the latter requires less redundancy. The latter approach, which is of our concern, may involve duplication of a system (or its modules) with comparison and/or using EDCs, providing the circuitry with the possibility of on-line detection of internal faults, and appropriate design of recovery procedures. Since various classes of such circuits can be distinguished, we will use a generic term selfchecking (SC) circuits to denote all of them. Self-checking design offers concurrent error detection (CED), i.e. error detection performed in real-time continuously with the system functioning, of both permanent and temporary (both transient and intermittent) faults. This technique supports achieving fault tolerance of a digital system for temporary faults, provided that the sequence of events: error detection, rollback recovery, and operation retry is sucessfully performed. This approach is particularly welcome in many digital systems, when we recall that: (1) nowadays more than 90% of faults which occur during system operation are temporary [182] and they are difficult to detect (if at all) by applying periodic software diagnostic test procedures; and (2) the use of EDCs and implementing circuits as SC is relatively inexpensive. However, it must be pointed out that using EDCs can be economically justified if and only if it results in significantly less overhead than duplication with comparison, which always introduces more than 100% redundancy: one extra module and a comparator. Also, one should not overlook that duplication usually involves significantly less design effort to be implemented than other SC techniques. Another important problem with designing and implementing any FT digital system is the presence of a hardcore, which can be loosely defined as that part of the hardware that must be functioning

correctly in order to initiate any diagnostic functions. The probability of hardcore failure can be reduced by using the following techniques: (i) minimizing the amount of hardware in the hardcore, e.g. by implementing circuits as SC or FT; (ii) implementing the hardcore using highly reliable components; and (iii) providing mechanism to facilitate periodic off-line testing the hardcore. A more extensive discussion of the hardcore problem can be found in [78].

The following recovery functions are performed within a FT system that uses fault detection and recovery, after a fault occurs. The first step in tolerating a fault is to detect an error produced as a result of it as soon as it is produced, before it propagates through the system. Once the fault is detected, the diagnosis whether the fault is permanent or temporary can be performed, e.g. through rollback and retry. In case of temporary fault, it is likely that the fault will disappear and the system may resume its operation without repair. Otherwise, it is assumed that a fault is permanent and its location up to a replaceable component is necessary for a possible reconfiguration of the system, which then may resume its operation, possibly with degraded performance.

The need for the use of coding techniques for providing digital systems with hardware means for on-line verification that the system operates correctly is very apparent from the wealth of applications of digital systems in which error-free computation is one of the key requirements. Once an internal fault occurs in the system, then it is desirable to detect it as quickly as possible. On one hand, the ever growing complexity of VLSI chips with decreasing size of internal devices makes modern digital systems more and more vulnerable to temporary faults. On the other hand, the decreasing price of hardware (relative to the cost of software development) justifies the use of hardware error handling techniques. The industrial experience of respected computer manufacturers such as Tandem Computers and Sun Microsystems proves that relying solely on the high reliability of VLSI integrated circuits and run-time checks to ensure data integrity of general-purpose microprocessor-based systems has become insufficient [61]. It is estimated that on average one out of 10000 personal computers per month experiences data corruption due to internal failures, which go undetected by commonly used traditional techniques of on-line error detection which rely on validity checks, parity control of the datapaths only, and ECCs of memory. It was explicitely pointed out that the densly packed VLSI chips are already so susceptible to intermittent and transient faults, that the minimum of error protection, such as provided by an EDC, of most modules of a digital system becomes mandatory. Therefore, there is a strong motivation to support less expensive techniques of tolerating temporary faults that rely on control flow checking (for an excellent survey, see [190]) by significantly stronger methods such as SC design.

A number of different classes of error control codes have been constructed for

error protection of digital systems [11], [46], [64], [65], [134], [160], [165], [207]. For many years the research of error codes has been motivated primarily by the needs of error-free data transmission [11], [64], [134]. However, since the requirements imposed on error codes used to implement FT computer systems are essentially different, their principal attributes are highlighted now.

- 1. Information is handled in parallel in a computer. This calls for efficient and fast encoding and decoding algorithms.

- 2. Encoding and decoding circuitry introduces extra delay and it should not slow down the system operation significantly.

- 3. Hardware needed for encoding and decoding should be relatively simple compared to hardware of functional circuitry (which performs 'useful' computation), since it not only increases the overall cost of a system but also the likelihood of a hardware failure (which will however be detected before undetected errors will be spread through a system).

- 4. Anticipated errors vary from one module of a digital system to another. This will require a clever selection of encoding which is most efficient to handle a particular class of errors.

- 5. Application of error codes to protect data which is only transferred from one place to another or is stored is relatively easy. The task becomes generally difficult when information is modified in some way (e.g. addition of two operands with an ALU generates new information—a sum and an overflow signal), since the error code used must be preserved under such operations.

- 6. Encoders and decoders themselves also cannot be assumed to be fault-free, and therefore they also should be implemented as FT circuits.

As for the EDCs (which are of our interest), four general classes of EDCs can be distinguished: parity codes, 2-rail and duplication codes, arithmetic codes, and unidirectional EDCs (UEDCs). Basic theory of EDCs and their applications for designing SC circuits can be found in any textbook on FT hardware [73], [78], [159], [164], [165], [182], and [207], whereas the state-of-the-art surveys were given in [96] and [145]. Unfortunately, selection of only one EDC which would be the best suited for a particular digital system, aimed at reducing the overall number of encoders and checkers throughout the system, is infeasible. It is well known that the error codes that are suitable e.g. to protect the bus or the RAM system are not preserved by the arithmetic circuitry, and conversely, error codes that are suitable to protect arithmetic circuitry may be too expensive to be used for the bus and not powerful enough to be used in memory (which generally requires using an ECC). Many other examples of such conflicting requirements can also be

given. Overall, error coding used to protect hardware of digital systems does not need to be sophisticated, and yet it should be capable of sufficiently protecting every module of a system at the minimum cost of extra hardware and/or delay.

Encoding data using EDCs and realization of circuits as SC may provide varying degree of protection against undetected faults and errors. The most stringent requirement formulated for SC design has been referred to as the totally self-checking (TSC) goal [188]:

the first erroneous output resulting from an internal fault of the digital circuit is detectable, i.e. it is a non-codeword.

This property is desirable in any digital system wherein increased confidence that a system is working correctly is of primary importance, i.e. it is preferable to stop the operation of a system rather than to allow it to produce an incorrect output.

The following advantages of TSC circuits are well known:

- 1. Any error caused by both permanent and temporary fault from a well defined class of likely faults is detected.

- 2. Errors are detected immediately after their first occurrence, which precludes the corruption of data in the system.

- 3. The amount of hardware in the hardcore of the computer system can be significantly reduced.

- 4. Recovery time of a system after error detection is significantly shortened, due to automatic fault detection and isolation. In particular, automatic replacement of a faulty module is feasible in a redundant and/or multiprocessor system.

- 5. Repair of a faulty system is facilitated and expedited.

- 6. Diagnostic software of a system can be significantly simplified, since SC design can be seen as a supplementary technique to off-line diagnosis.

The Electronic Switching System (ESS) by Bell Labs., built in the sixties, is the first example of a complex digital system for non-military and non-space applications wherein most modules were built as SC for high availability [10], [24], [78], [191], [199]. Many experimental SC processors and complex SC modules, most of which were partially protected by various UEDCs, have been proposed since then: [25], [37], [45], [56], [57], [95], [111], [121], [132], [169], [170], [180], [207], [211], [212], and [213]. Renewed growing interest in practical applications of SC circuits is exemplified by two most recent commercial products: the large

mainframe IBM Enterprise System/9000 [184] and the on-board processor by Harris Corp. [63]. The modules of either system are protected against undetected errors by a combination of parity, duplication, residue mod 15, and m/n encodings, depending on the type of a module. Also, there are already known multiprocessor systems composed of up to 100,000 processors which use SC modules to provide for fault-tolerance and reconfiguration, see e.g. [29]. Clearly, the design of SC digital circuits is an important area of fault-tolerant computing (FTC), attractive not only from a theoretical but also from a practical point of view, which has experienced significant growth of interest in the computer industry in recent years.

Unfortunately, despite declining cost of hardware and many unquestionable advantages, SC circuits have been rather sparingly used in commercial computers, due to increase of chip area and extra delay, which are regarded too high by most computer manufacturers. Hence, the most important factors which could make SC circuits an economically feasible alternative for implementation of future FT systems are: (1) availability of EDCs with low redundancy but capable of detecting the most likely errors; (2) readily-available and efficient implementation methods of EDCs in digital hardware of any type; and (3) availability of fast and low-cost encoders and checkers.

## 1.2. The Scope of this Work

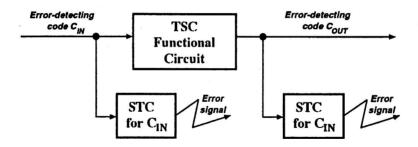

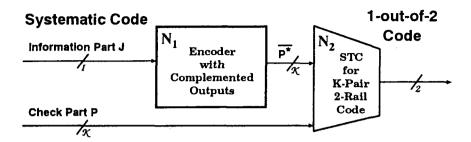

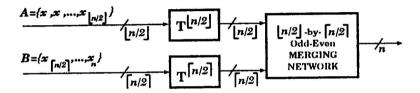

A general scheme of the TSC system (given in Fig. 1.1) consists of two types of blocks: a functional circuit that executes some 'useful' function, and two checkers whose only function in a digital system is to monitor whether the inputs entering and the outputs generated by a functional circuit are correct or not. The checkers are a pure overhead in the system: should there be no faults in the system, no checker would be needed. The first step in implementing a TSC system is to encode input and output data using some EDCs  $C_{IN}$  and  $C_{OUT}$ , respectively.  $C_{IN}$  ( $C_{OUT}$ ) can be seen as a proper subset of all  $2^n$  ( $2^s$ ) binary input n-tuples (output s-tuples) selected in such a way that they have some common attribute which is easy to verify, so that every occurence of an input codeword  $X \in C_{IN}$  and an output codeword  $Z \in C_{OUT}$  is interpreted as correct operation of the system. Every occurence of a non-codeword  $X^e \notin C_{IN}$  or  $Z^e \notin C_{OUT}$  is a symptom of incorrect operation of the system, which should be promptly signaled by the checkers to some external control unit of the system. A special circuit called a checker for a code  $C_{IN}$  (and  $C_{OUT}$ ) must be built to determine if the output of the circuit it checks is a codeword or not, by proper setting of its error indication signal. However, the simplest 1-output checker whose output is z whenever a

Figure 1.1. General scheme of the self-checking system

codeword is present, and  $\overline{z}$  when a non-codeword is present,  $z \in \{0,1\}$ , contains a hardcore: any internal fault sticking its output at z would never be detected and the checker would loose its checking capabilities. (Note that any internal fault sticking its output at  $\overline{z}$  is always detected.) This is one obvious reason that to upgrade the reliability of a checker, it should have at least two outputs encoded in an EDC. Usually, a checker output of (01) or (10) indicates correct operation, whereas (00) or (11) indicates an input error or an internal fault. Additionally, the 2-output checker should be designed and implemented in such a way that no realistic single fault of some set of faults F sticks its output at  $(z\overline{z})$ . However, even then the same undesirable effect of checker output stuck at  $(z\overline{z})$  can be caused by the occurrence of the sequence of one latent fault followed by another fault, both from F. A checker implemented as self-testing (ST) for F is a circuit wherein the latter problem virtually does not occur, provided that all codewords from  $C_{IN}$  ( $C_{OUT}$ ) occur frequently enough, so that every fault in F is detected before another fault from F occurs. To achieve the TSC goal, the functional circuit must be implemented as TSC for a set F of the most likely internal faults. In a TSC circuit, no fault in F can cause an undetectable error in normal operation and all faults in F are tested by incoming codewords from  $C_{IN}$ . In the latter case, for some codeword  $X \in C_{IN}$  a fault causes a non-codeword output  $Z^e \notin C_{OUT}$ , which is detected by the output checker. Therefore, the system from Fig. 1.1 is free of hardcore, provided that there occur no faults other than those for which the functional circuit is TSC and the checkers ST. More formal and detailed presentation of these topics will be given in Section 3. This monograph deals with the design methods of combinational self-testing checkers (STCs) for several classes of UEDCs.

A unidirectional error (u-error) is a multiple error such that all erroneous bits are of either  $0\rightarrow 1$  or  $1\rightarrow 0$  type, but not both at the same time. Unidirectional errors have been observed as the result of power failures [160], the failures in byte-serial memory systems [52], [128], [206], [207], in regular VLSI circuitry

such as ROM memory systems [45], [46], [101], [122], [160] and Programmable Logic Arrays (PLAs) [94], [123], [116], [213], in laser compact disks [46], [87], and many other [22], [24], [121], [122], [158], [160], [172]. Unidirectional errors may also occur due to single and multiple unidirectional faults occurring in *inverter-free (IF)* (i.e. using AND and OR gates only) combinational circuits using shared logic [35], [119], [185].

The u-errors of any multiplicity are detected by so called unordered codes such as, for example, m/n codes and Berger codes which were proved to be the optimal nonsystematic and systematic unordered codes in [44] and [9], respectively. Many other optimal systematic unordered codes equivalent to Berger codes were defined by Ashjaee and Reddy [5], [6], and Piestrak [151]. However, the data used in a digital system are in many cases organized in bytes and stored, transmitted or transformed by separate units operating on bytes. Therefore, provided that only single hardware failures can occur and are confined to independent units, instead of u-errors of any multiplicity only up to t u-errors are the most likely to occur (t is the byte length). Also, the multiplicity t of the output u-error in certain circuits using shared logic (e.g., a PLA [119]) can be inherently limited by their internal structure. As a result, instead of an unordered code a less redundant (and hence cheaper) t-UEDC can be used. The optimal (nonsystematic) t-UEDCs were proposed by Borden [14]. Systematic t-UEDCs were first proposed by Dong [38], and then improved by Bose and Lin [17] and Jha and Vora [71]. Further savings in the codeword length are possible when a burst error model is assumed. (A burst error of length b means that the erroneous bits are confined to a cluster of b adjacent bits.) Burst unidirectional error detecting codes (BUEDCs) were proposed by Bose [15] and Blaum [12]. Byte unidirectional error detecting codes were proposed by Bose and Lin [15], [18], and by Dunning et al. [40], [41]. Finally, let us mention for completeness about the abundant number of systematic codes capable of correcting d random (symmetric) errors and detecting all or t u-errors (d-EC/AUED and d-EC/t-UED codes) which have also been studied extensively in recent years, see e.g. [13] and [124], but are beyond the scope of this work. Since all the above mentioned codes have in common that they are capable of detecting u-errors of a given multiplicity t, henceforth we shall call any of them with a single generic term unidirectional error detecting code (UEDC).

Numerous applications of UEDCs to implement SC and FT digital modules, which have been reported continuously throughout years, include:

- Microprogram control units: [24], [34], [56], [78], [132], [191], [199], [207], and [211].

- Synchronous sequential circuits: [22], [32], [33], [35], [49], [55], [72], [82], [97], [102], [110], [127], [158], [175], [177], [195], [196].

- Asynchronous sequential circuits: [27], [50], [93], [100], [112], [126], [176], [177].

- PLAs: [19], [45], [94], [120], [123], [163], [209], [212] and semiconductor ROMs [46], [101], [160], [213]; and

- Arithmetic circuitry: arithmetic-logic units (ALUs) [91], multipliers and dividers [92], and floating-point arithmetic units [89].

The growing interest in *u*-error detecting and correcting codes is confirmed by their first commercial applications recently reported in [46]: in FT 4-Megabit VLSI ROMs for yield improvement and in large area laser compact disks for defect tolerance, both by NTT.

Among UEDCs, unordered codes deserve special attention. First, the circuits both combinational [111] and sequential [110] can be easily implemented to achieve the TSC goal, provided that unordered codes are used in all interfaces and all combinational circuitry is realized IF (which is quite natural when unordered codes are used) [93]. Secondly, such classes of self-timed (asynchronous) circuits as speed-independent and delay-insensitive circuits must use unordered codes for data encoding to enforce their correct operation independently of delays (in gates and wires, respectively) and the by-product is that they are also SC for some faults: [4], [201], [202], [203]. The most recent study of these topics we have presented in [156]. Finally, an extremely important practical application of certain m/n codes (called balanced codes) and circuitry supporting their use was revealed recently in [129] and [193], where they were used for noise reduction across VLSI input/output pins.

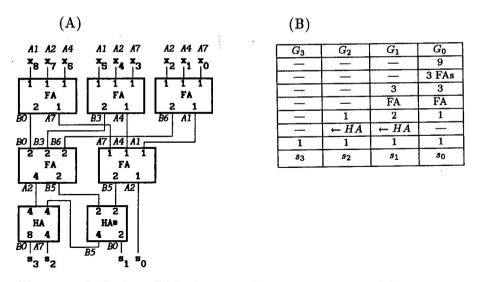

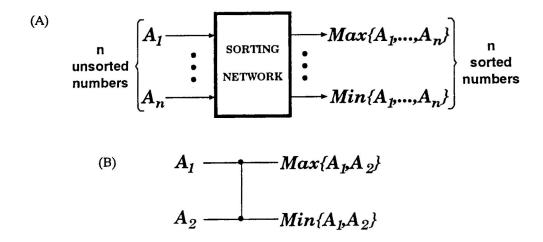

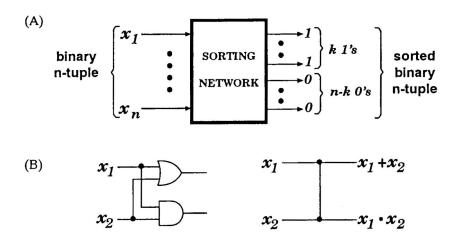

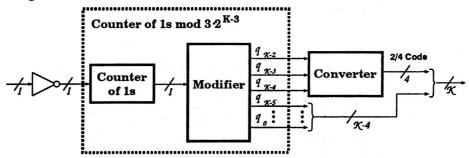

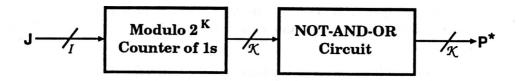

Nonsystematic UEDCs such as m/n codes and Borden codes have in common that checking whether a binary n-tuple X is a codeword can be done by determining the weight of X (i.e. the number of 1s in X). Similarly, all systematic UEDCs mentioned above have in common that the check bits which are responsible for providing the code with u-error detecting capabilities are generated on the basis of the weight of the remaining part of a codeword which is: (i) an information part — for a code which is UED only, and (ii) a codeword of some d-EC code — for a code which is d-EC/AUED or d-EC/t-UED. Thus, the availability of the efficient counter of 1s (i.e. a circuit that generates the weight of a binary vector) as well as any other combinational circuit that efficiently realizes an arbitrary logic function that depends on the weight of an input vector (e.g. a threshold circuit), is of crucial importance while designing circuitry supporting the use of all UEDCs.

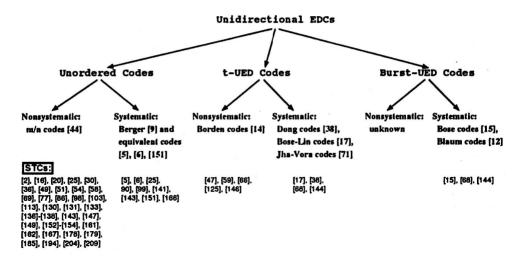

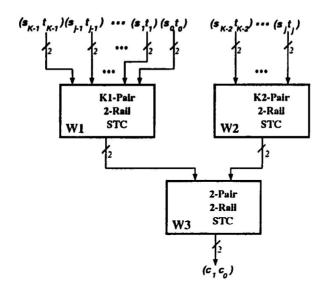

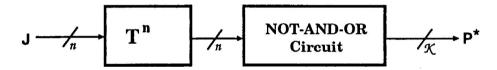

To date, there have been several design methods for the STCs for almost all classes of UEDCs which, however, have not taken explicitly into account the common attribute such as the dependence of the checker functions on the weight

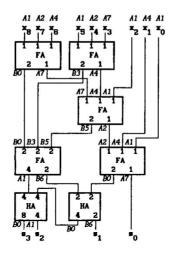

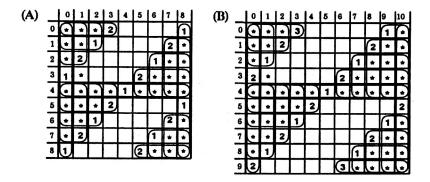

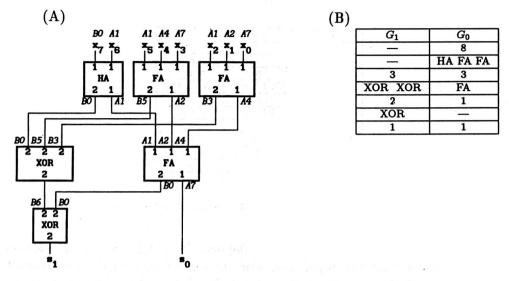

Figure 1.2. Survey of the most important UEDCs and design methods of STCs for these codes

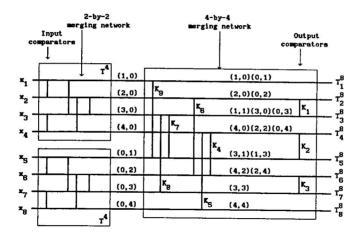

of an input vector. This observation can be derived from the following general survey of the existing design methods for the STCs for UEDCs. Firstly, note that many STCs for m/n codes (m > 1) built using threshold circuits [2], [49], [54], [98], [167], [177], [178], [179], and [204] have used only two realizations of the multioutput threshold circuits: a prohibitively complex (for larger n) twolevel version or less complex multilevel cellular version from [168]. Later the so called completely bifurcated threshold circuits were considered in [42]. [136]. and [137]. All these threshold circuits have the number of gates and gate inputs which is at least  $O(n^2)$ . This happened because the superb performance and testability of the multioutput threshold circuits implemented as sorting networks (SNs) was discovered only recently by the author [143], [148]. Secondly, there have been STCs for various classes of UEDCs using the counters of 1s which were built using the so called parallel counters (entirely composed of full-adders (FAs) and half-adders (HAs)) [6], [15], [17], [36], [68], [71], [99], [131], [133]. Only two realizations of parallel counters have been suggested to build encoders and decoders in all the literature on designing FT hardware and on systematic UEDCs with error-correcting properties (including the most recent works [68] and [124]): the basic realization given in [3] and its modification for easy testability suggested in [99]. Both employ a number of carry-propagate adders (CPAs) which introduce unnecessarily large delay. To date, significantly faster and in some cases less complex parallel counters that have been suggested in the voluminous literature on multipliers [26], [43], [76], [104], [192], [208] have clearly been overlooked. Finally, there have been some systematic t-UEDCs for which the STCs have not been constructed yet — see [17] and [71]. For readers' convenience, the

classification of the most important UEDCs that will be considered here and the survey of design methods of STCs for these codes are shown in Fig. 1.2.

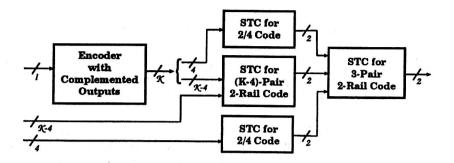

In this monograph, we aim to present systematic design for combinational STCs for UEDCs. It summarizes and extends the results on related topics that we have presented in several earlier works [136]–[156]. We shall show that the STCs for the most important known UEDCs can be designed by using two essentially different but complementary basic building blocks: a multi-output threshold circuit and a parallel counter. The design procedures will be presented independently of any particular technology of VLSI integrated circuits, since their fast development would easily make any technology-dependent considerations obsolete. Nevertheless, we shall concentrate on those realizations which take into account some attributes which are common for most modern VLSI technologies such as low fan-in and fan-out, repeatability of basic modules, regular structure, and easy testability. In this context, the emphasis will be given on the STCs which offer hardware efficiency and/or small delay.

This monograph is organized as follows. Section 2 introduces the fault and error models applicable to digital VLSI circuits. Then the basic characteristics of the EDCs are presented. A particular emphasis is on the thorough analysis of error detecting properties of various UEDCs and their definitions.

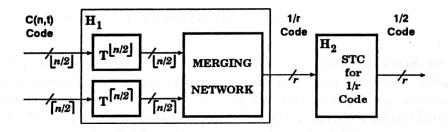

Section 3 contains a systematic presentation of the basic theory of SC combinational circuits. Special attention is given to the properties of STCs and the basic assumptions regarding the fault/error behavior of a SC digital system. It is concluded with the presentation of the so called 'normal checker' — a universal general structure of an STC suitable for any systematic EDC. Its structure justifies why both the encoders and STCs for systematic EDCs are considered here together: an encoder can be used as an integral part of an STC for the same code.

Section 4 presents the detailed survey of various counters of 1s which will be used as the basic building blocks in almost all circuits presented here. Two major classes of the counters of 1s are presented separately: parallel counters and the multi-output threshold circuits.

The next three sections present the design methods of the STCs for nonsystematic UEDCs and both encoders and STCs for systematic UEDCs. We have concentrated on the methods which provide the most hardware-efficient and fast circuits. The testability of these circuits is also analyzed in details.

Section 5 covers the design of the STCs for selected m/n codes — those which are the most important from a practical point of view. Included are the m/2m and m/(2m+1) codes (which are the optimal unordered codes as they offer the maximum capacity for a given codeword length n and are capable of detecting u-errors of any multiplicity), the 2/n codes, and the 1/n codes.

Section 6 presents the design of STCs for nonsystematic Borden codes, which are the optimal t-UEDCs. It is shown that the least complex albeit the fastest STCs can be built on the basis of two multioutput threshold circuits. We have derived the logic functions of an STC for any Borden code expressed in terms of the threshold functions.

Section 7 presents the design of both the encoders and the STCs for various classes of UEDCs. For all codes considered in this section, the two versions of both the encoders and the STCs are presented: one version is built on the basis of a parallel counter, whereas the other employs a multioutput threshold circuit. Subsequently are presented the encoders and STCs for: the optimal systematic unordered EDCs (i.e. the Berger codes and some codes equivalent to them), three classes of t-UEDCs, and the optimal BUEDCs. The STCs for two classes of systematic t-UEDCs are the first ever proposed.

The monograph is concluded with Section 8 containing summary and applications of the results given here. Also, suggestions for further advancement of the concepts presented here and some related open research problems are discussed.

#### 2. ERROR DETECTING CODES (EDCs)

In this section we shall present the basic fault and error models, the main characteristics of EDCs, and the definitions of the most important classes of UEDCs in the order from the most to the least redundant.

# 2.1. Faults and Errors in Digital Circuits

Here we are concerned exclusively with digital circuits whose incorrect operation can be analyzed on the logic level (i.e. parametric faults such as the change of current drawn by the circuit or a delay fault are excluded). The terminology presented here is based on [85], [165], and [182].

**Definition 2.1.** A failure occurs in a digital circuit when its behavior deviates from the specified behavior, i.e. when it is unable to perform its designed logic function.

The failures are considered on a physical level of a circuit: e.g. a line shorted to the ground, two lines shorted together, a broken line, a shorted diode or transistor.

**Definition 2.2.** A fault is an incorrect logic state of a line of a digital circuit resulting from failures of its components.

The faults are considered at the *logical level* of abstraction. A given fault may result from various failures. The most commonly used is the stuck-at-z (s/z),  $z \in \{0,1\}$ , fault model which assumes that the logic value on an input or output line of a circuit is set to z, independently of the binary vector applied to the input of the circuit. There are also several faults which are typical either for a particular technology (e.g. stuck-open and stuck-on faults in CMOS) or for a particular class of circuits (e.g. adjacent line faults and crosspoint faults in PLAs and pattern-sensitive faults in RAMs), but none of them will be considered here.

Further classification of faults may include the multiplicity of faults (single and multiple faults) and the time of duration (temporary and permanent faults). Usually, and in this monograph too, it is preliminarily assumed that only single s/z faults occur. This assumption is justified because of two reasons: 1) only single faults are algebraically tractable without excessive computations; and 2) the test sets capable of detecting single s/z faults have been proved to have very high fault coverage of multiple faults as well [1], [80]. However, it will be shown later that most parts of many checkers considered here are tested exhaustively by applying codewords only, and therefore the checkers are actually ST for many multiple combinational faults as well. Temporary faults, which have been predominant in modern digital systems [182], can originate from the external physical environment — transient faults, or can result from internal (with respect to a circuit) causes — intermittent faults. Transient faults are those caused e.g. by power supply fluctuation, electromagnetic perturbations, temperature and humidity variations, air pollution, vibrations, and radiation. Intermittent faults result from the presence of rarely occurring combinations of conditions such as: changes in the parameters of a hardware component (e.g. effect of temperature variation, delay in timing due to parasitic capacitance), loose connections, pattern-sensitive faults in semiconductor RAM, or when a system load goes beyond a certain level. Although temporary faults do not damage the circuits involved, they cause errors which are extremely difficult to detect (due to their temporary nature) unless the CED techniques based on using EDCs and implementing the circuits as SC are used.

**Definition 2.3.** An error is the occurrence of an incorrect logic state caused by a fault within a circuit, which may occur in some other place than a fault site.

The errors are considered at the *informational level* of abstraction and are characterized by the register values. The types of errors which occur in modern memory, logic, and arithmetic VLSI circuits as well as in non-semiconductor memory systems are many and varied. They can be broadly classified as *symmetric* (single or multiple), multiple *unidirectional*, and multiple *asymmetric* errors. In the sequel we refer to the transition  $0\rightarrow 1$  as 0-error and  $1\rightarrow 0$  as 1-error.

**Definition 2.4.** If both 0-errors and 1-errors occur in a received word with equal probability then the errors are called symmetric.

**Definition 2.5.** If both 1-errors and 0-errors can occur in received words, but in any particular word all errors are of one type, then they are called unidirectional.

**Definition 2.6.** If the probability of unidirectional z-errors is extremely small compared to unidirectional  $\overline{z}$ -errors,  $z \in \{0,1\}$ , the errors are called asymmetric.

Symmetric errors are quite common in many digital systems and hence their sources need not be specified here. u-errors have been observed as a result of permanent failures such as: power supply failure, stuck-at faults in shift register memories, faults typical for PLA and ROM, large-area digital compact disks [24], [191], [206], [128], [160], [94], [122], [45], and [46]. They also occur as a result of single (or multiple unidirectional) s/z faults in IF combinational circuits using shared logic. Finally, asymmetric errors occur in optical communication (spurious photons cannot be generated) and as a result of some failures in a class of ROMs [46], [65], [101]. Obviously, the analysis shows that unidirectional or asymmetric errors may occur: in a single line, in a single byte, in a part of the storage area, or as a burst of a particular length. In each case an appropriate code, capable of detecting a particular class of the most likely errors, should be used for protection.

Here we are concerened with u-errors only. The u-errors can be classified from the most to the least difficult to detect as follows: a) any multiplicity; b) up to t errors; c) burst errors of length b; and d) byte errors.

**Definition 2.7.** A burst error of length b is any pattern of errors which is confined to a b-bit portion of the word.

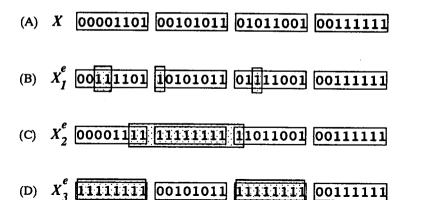

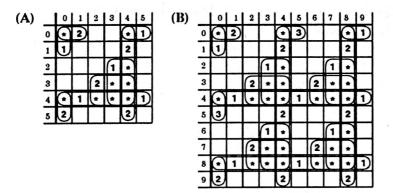

Let  $X=(x_{31}\ldots x_1x_0)$  be composed of four bytes, i.e.  $X=(B_3B_2B_1B_0)$ , where  $B_3=(x_{31}\ldots x_{24}),\ B_2=(x_{23}\ldots x_{16}),\ B_1=(x_{15}\ldots x_8),$  and  $B_0=(x_7\ldots x_0).$  The examples of three types of *u*-errors are given in Fig. 2.1

## 2.2. Basic Properties of EDCs

Let C denote the set of codewords, I — the number of information bits, n—the length of the codeword, and K—the number of check bits (K = n - I). The following characteristics of a code are taken into account while selecting

an EDC for a particular application:

1. Class of errors detected.

Figure 2.1. Three types of u-errors: Sample codeword (A); 4-unidirectional  $0 \rightarrow 1$  error (i.e. t=4) (B); Burst unidirectional  $0 \rightarrow 1$  error (i.e. b=11) (C); 2-byte unidirectional  $0 \rightarrow 1$  error (in bytes  $B_1$  and  $B_3$ ) (D)

- 2. Redundancy of a code, characterized either by the number of redundant bits K, or the rate (or efficiency) of the code expressed by the ratio I/(I+K).

- 3. The *capacity* of the code denoted with |C|, i.e. the number of codewords, given a codeword length n.

- 4. Systematicity and separability of a code: in both a systematic and a separable code the information bits can be distinguished from the check bits. In a separable code, additionally, the information parts and the check parts of the operands can be processed in parallel by a SC functional circuit. Generally, for a given n and a given class of errors, the capacity of a nonsystematic code is larger than that of a similar systematic code. However, despite this advantage, nonsystematic codes have found limited applications due to significantly more complex encoding and decoding hardware than their systematic counterparts. In particular, decoding of a systematic codeword relies on neglecting its check part, which is not the case in any nonsystematic code. Nevertheless, there are some notable example applications wherein nonsystematic codes can be used efficiently: the state assignments and input/output encodings of sequential machines and many PLA-based control circuits.

- 5. Speed and complexity of the encoding and checking circuitry.

- 6. Availability of efficient design methods of SC hardware using an EDC. This

is not a problem as long as non-transforming modules are concerned, such as memory, a bus, or a multiplexer. However, it can be a serious problem when transforming modules are concerned, e.g. an ALU or a control unit.

- 7. The overall cost of implementing a code in a system which can be measured by:

- (a) The number of extra inputs and outputs of an integrated circuit or a printed circuit board.

- (b) The amount of extra hardware required to implement an encoder, a checker, and a functional circuit modification, which can be measured by: the number of extra gates and/or gate inputs (or transistors), or by the amount of extra chip area.

- (c) The extra delay caused by necessity of using an encoder and a checker, as well as due to the functional circuit modifications.

#### 2.3. Unordered Codes

The partial ordering on the binary n-tuples is defined as

$$X \leq Y$$

iff  $x_i \leq y_i$  for all i.

For example,  $(1,0,0,1) \le (1,1,0,1)$  and  $(1,0,0,1) \not \le (0,1,0,1)$ .

**Definition 2.8.** Let X and Y be two binary n-tuples. We say that X covers Y (written  $Y \leq X$ ) if and only if X has 1s everywhere Y has 1s. If neither  $Y \leq X$  nor  $X \leq Y$ , then we say X and Y are unordered (written  $X \not\subset Y$ ).

In later discussions the relation < will be used whenever  $Y \le X$  and  $Y \ne X$ .

**Definition 2.9.** A set of binary n-tuples C is called unordered code if for every  $X, Y \in C$ ,  $X \neq Y$  implies  $X \not\subset Y$ .

Thus, an unordered code is one in which no codeword covers some other codeword. In [185] it was shown that a code C is able to detect all u-errors if and only if it is unordered.

## 2.3.1. Nonsystematic m/n Codes

**Definition 2.10.** An m-out-of-n code (m/n) code, constant-weight code) is one in which all valid codewords have exactly m 1s and n-m 0s.

The set of all m/n codewords will be denoted with  $C_{m/n}$  and its capacity equals to  $|C_{m/n}| = \binom{n}{m}$ . The  $\lfloor n/2 \rfloor/n$  code is the optimal unordered code [44], in the sense that there is no other unordered code of codeword length n which has more codewords than the  $\lfloor n/2 \rfloor/n$  code.

#### 2.3.2. Systematic Unordered Codes

**Definition 2.11.** The optimal systematic unordered code (OSUC) is one which uses the fewest number of redundant check bits.

The optimal systematic unordered code was first defined by Berger [9].

**Definition 2.12.** The Berger code  $C_{(I,K)}$  is a systematic code wherein the K check bits  $P_X$  are the binary representation of the count of the I information bits  $J_X$  which are 0s, where  $K = \lceil \log_2(I+1) \rceil$ . (An alternative equivalent Berger code has the check part  $P_X$  defined as the bit-by-bit complemented number of 1s in the information part  $J_X$ .)

**Definition 2.13.** [5] A Maximal Length Berger (MLB) code  $C_{MLB(K)}$  is one for which  $K = \log_2(I+1)$ , i.e.  $I = 2^K - 1$ .

Henceforth we shall use the following concept of concatenated codes introduced in [185], which differs from the concatenated codes known from coding theory [134].

**Definition 2.14.** The concatenation of a vertex U with u coordinates and a vertex V with v coordinates is a vertex W = UV with u + v coordinates whose first u coordinates are identical to those in U, and whose last v coordinates are identical to the coordinates in V.

**Definition 2.15.** The concatenation of two codes  $C_U$  and  $C_V$  of capacity  $|C_U|$  and  $|C_V|$ , respectively, is a code  $C_W = C_U \times C_V$  of capacity  $|C_W| = |C_U| \cdot |C_V|$  which is formed by concatenating each vertex in  $C_U$  with every vertex in  $C_V$ .

**Definition 2.16.** A code C of length n is called equivalent to Berger code  $C_{(I,K)}$  if and only if n = I + K, it is systematic, unordered, and has the same number of codewords as  $C_{(I,K)}$ .

The codes equivalent to Berger codes were derived by Ashjaee and Reddy [5], [6], and recently by us [151], whereas some other non-optimal unordered systematic and nonsystematic codes can be constructed according to Mak [94]

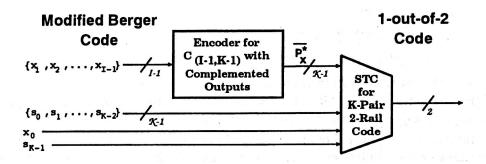

and Smith [186]. The modified Berger codes from [5] are defined for  $I=2^{K-1}$  (only) as the concatenation  $C_{MLB(K-1)} \times C_{1/2}$ , where two bits of a 1/2 codeword represent  $x_0$  — the least significant bit (LSB) of the information part, and  $c_{K-1}$  — the most significant bit (MSB) of the check part. The codes from [6] and [151], which can be constructed for any  $I \geq 4$  and for many  $I \geq 6$  (but not all), respectively, have the property that all  $2^K$  check parts are used (unlike in Berger codes with  $I \neq 2^K - 1$ ). This property allows to speed up one part of an STC for this code — an output STC for K-pair 2-rail code (see Subsection 3.4). However, the codes from [151] also have the closure property, which is necessary to build a PLA-based STC and also allows one to build an IF STC for this code.

Finally, we should mention one important class of systematic unordered codes—the 2-rail codes.

**Definition 2.17.** A K-pair 2-rail code is one which uses K check bits which are the bit-by-bit complements of the I = K information bits.

A K-pair 2-rail code is nothing else but a special case of an incomplete K/2K code with only  $2^K$  out of  $\binom{2K}{K}$  all codewords used. It is the most redundant unordered EDC (100% redundancy), but its main advantage is that the TSC circuits using 2-rail code are generally easy to implement in hardware. Here, 2-rail codes are important, since an STC for various systematic EDCs C can be easily constructed by translating C into a 2-rail code [6], [207]. The most prominent example is the well known normal checker (shown here later in Fig. 3.1) which is conceptually the simplest structure that can be used to implement an STC for any systematic code. The topic of designing STCs for specific incomplete UEDCs is not considered in this paper. For more details, an interested reader may refer to [30], [152], [153], [194] — about the STCs for incomplete m/n codes, and to [151] — about the STCs for incomplete OSUCs.

# 2.4. Other Unidirectional EDCs (UEDCs)

#### 2.4.1. t-UED Codes

The data used in a digital system are in many cases organized in bytes and stored, transmitted or transformed by separate units operating on bytes. Therefore, provided that only single hardware failures can occur and are confined to independent units, instead of u-errors of any multiplicity only up to t u-errors are the most likely to occur (t is the byte length). Also, errors caused by single faults in IF combinational circuits with shared circuitry may cause output u-errors of a limited multiplicity — up to some t, whose value depends on the maximum of

outputs which depend on signal on some line of the circuit, e.g. PLAs [19]. As a result, in all the above cases a less redundant (and hence cheaper) t-UEDC can be used instead of an unordered code.

Let n denote the codeword length and t the multiplicity of u-errors detected by a code.

**Definition 2.18.** A binary code C of codeword length n is called t-unidirectional EDC (t-UEDC) if no set of t u-errors can transform a codeword into another codeword.

#### A. Borden t-UEDCs

**Definition 2.19.** A Borden code C(n,t) is a code which is the union of all m/n codes whose weight is congruent to  $\lfloor n/2 \rfloor \mod (t+1)$ , i.e.

$$C(n,t) = \bigcup_{m=\lfloor n/2 \rfloor \mod (t+1)} C_{m/n} . \tag{2.1}$$

The nonsystematic code C(n,t) was defined by Borden [14] and shown to be the optimal t-UEDC. Its capacity is given by

$$|C(n,t)| = \sum_{m = \lfloor n/2 \rfloor \mod (t+1)} {n \choose m}.$$

(2.2)

In particular, it was shown [14] that

$$|C(n,2)| = \begin{cases} (2^n + 2)/3 & \text{for even } n, \\ (2^n + 1)/3 & \text{for odd } n; \end{cases}$$

(2.3)

and

$$|C(n,3)| = \begin{cases} 2^{n-2} + 2^{(n-2)/2} & \text{for even } n, \\ 2^{n-2} + 2^{(n-3)/2} & \text{for odd } n. \end{cases}$$

(2.4)

The C(n,t) code allows for any t from the interval  $1 \le t \le \lceil n/2 \rceil$ . Two extreme cases of the C(n,t) code are: (i) for t=1—the parity code which is systematic, unlike any other Borden code, and (ii) for n=2t—the constant-weight t/2t code, which are optimal codes capable of detecting all single errors and all u-errors, respectively. (Note that three classes of codes, usually considered separately, can be defined in this simple uniform way.)

#### B. Systematic t-UEDCs

Systematic t-UEDCs were first proposed by Dong [38], and then the optimal t-UEDCs were given by Bose and Lin [17] and Jha and Vora [71]. In the Bose-Lin

codes t is fixed for a given K, whereas in the Jha-Vora codes t also depends on I. As a result, for  $K \geq 5$  the Jha-Vora codes are capable of detecting more u-errors for some I. Note however that any t-UEDC has fewer check bits K (i.e. it is less redundant) than a Berger code (which is the optimal AUEDC) for  $I \geq 2^K$  only.

Let  $p_0$   $(p_1)$  denote the number of 0s (1s) in the *I*-bit input vector. Two following codes were given by Bose and Lin.

#### Bose-Lin Code 1

- (i)  $K \in \{2,3\}$ :  $J = p_0 \mod 2^K$ . The code detects t = K u-errors.

- (ii)  $K \geq 4$ : let  $J' = p_0 \mod 2^{K-1} = (q_{K-2} \dots q_1 q_0)$  be the tentative check part. From J' the final check part  $J = (s_{K-1} \dots s_1 s_0)$  is derived, where  $s_{K-1} = q_{K-2}, s_{K-2} = \bar{q}_{K-2},$  and  $s_j = q_j$  for any other j. Now the code detects up to  $t = 2^{K-2} + K 2$  u-errors.

Code 1 is optimal systematic t-UEDC for K = 2, 3, and 6 when it is capable of detecting t = 2, 3, and 6 u-errors, respectively.

#### Bose-Lin Code 2 (for $K \geq 5$ only)

First,  $J' = p_0 \mod (3 \cdot 2^{K-3}) = \{q_{K-2}, \dots, q_1, q_0\}$  is formed. Then, three MSBs  $(q_{K-2}q_{K-3}q_{K-4})$  which are  $(000), \dots, (101)$  are mapped one-to-one into  $(s_{K-1}s_{K-2}s_{K-3} s_{K-4})$  as six 2-out-of-4 codewords. The final check part  $J = \{s_{K-1}, \dots, s_1, s_0\}$  consists of the latter four bits as MSBs and unchanged K-4 LSBs from J'. Code 2 detects up to  $t \leq 5 \cdot 2^{K-4} + K - 4$  u-errors, i.e. t is larger than for Code 1.

#### Jha-Vora Codes

The Jha-Vora codes are capable of detecting more u-errors than the Bose-Lin codes with the same K for  $2^K \leq I < k \cdot 2^K$ , where  $k \leq 1.45$  and it varies with I and K (see Table 2 in [71]). They have a rather sophisticated structure of check parts assignment, which can be done by the following algorithm.

#### Algorithm 2.1.

- 1. Let  $K = \lfloor \log_2 I \rfloor$ . Set  $l = I 2^K + 1$ .

- 2. Derive the set  $S(K) = \bigcup_{j=0}^{\lfloor K/2 \rfloor} C_{(\lfloor K/2 \rfloor j)/K}$  and arrange the binary K-tuples within S(K) according to their decreasing decimal value. The i-th word of an ordered set S(K) is denoted with  $C_i(K)$ ,  $1 \le i \le l$ .

Figure 2.2. Codeword format of a Blaum's BUEDC

- 3. Derive the sets  $B_i(K) = A_i(K) \setminus \{A_i(K) \cap \{\bigcup_{j=i+1}^l A_j(K)\}\}, 1 \le i \le l-1$ , and  $B_l(K) = A_l(K)$ , where  $A_i(K) = \{X \mid X \in S(K) \text{ and } X < C_i(K)\}$  and  $A_{l+1}(K) = \emptyset$ .

- 4. Derive the set  $Y = \{X \mid X \in \{0,1\}^K \text{ and } X \in \bigcup_{i=1}^l A_i(K)\}$ , wherein all K-tuples are ordered according to their decreasing decimal value.

- 5. Derive a sequence Z of check parts Y,  $C_1(K)$ ,  $B_1(K)$ ,  $C_2(K)$ ,  $B_2(K)$ ,...,  $C_l(K)$ ,  $B_l(K)$  which are to be assigned successively to subsets of information parts of weights I, I-1,..., 0.

Note: If two or more sets have common elements, the sequence includes each instance of the common elements.

6. Find the maximum multiplicity of u-errors detected by this code

$$t = \min_{i, 1 < i < l} \{ p_2(C_i(K)) - p_1(C_i(K)) - 1 \},$$

where  $p_1(C_i(K))$  and  $p_2(C_i(K))$  denote the numbers of positions in which  $C_i(K)$  occurs.

For more details on Jha-Vora codes, an interested reader may refer to [71].

# 2.4.2. Burst-UED Codes (BUEDCs)

Faults in certain semiconductor memory systems tend to produce bursts of u-errors. Hence, codes capable of detecting bursts of a certain length using a minimum number of check bits are important, since further savings in the codeword length are possible (compared to both unordered codes and t-UEDCs).

To date, no nonsystematic burst UEDCs (BUEDCs) have been proposed. The optimal systematic BUEDCs were first proposed by Bose [15] and then improved by Blaum [12]. Given a sufficiently large number of information bits I, let b(K) denote the maximum length of a burst that a systematic BUEDC can detect with K check bits. The Bose BUEDCs have  $b(K) = 2^{K-1}$ . The Blaum codes were shown more effective than t-UEDCs for  $K \geq 3$  and  $I \geq 2^K$ . Compared to Bose BUEDCs, the Blaum codes are: (i) equivalent for  $K \in \{2,3\}$ , since they also have  $b(K) = 2^{K-1}$ , and (ii) more efficient for  $K \geq 4$ , since they have  $b(K) > 2^{K-1}$ :

for instance, b(4) = 9 > 8, b(5) = 19 > 16, and b(6) = 41 > 32. Hence we shall concentrate on the more efficient Blaum codes.

Check part assignment for the Blaum codes is easy for a given K. Suppose that check parts are assigned to the groups of information I-tuples with 0, 1, ..., and I 1s. The check parts, which are assigned subsequently and cyclically to these ordered groups, are the following: the all-1s K-tuple, K K-tuples of weight K-1 ordered increasingly according to their decimal values,  $\binom{K}{K-2}$  K-tuples of weight K-2 etc., etc., the all-0s K-tuple which is followed again by the all-1s K-tuple, etc. Obviously, the sequence of check parts eventually repeats for every subsequent sequence of  $2^K$  groups. An example of this encoding is given in the third column of Table 7.5 for K=3 and any  $I\geq 8$ . The bits in a codeword X of a Blaum BUEDC are arranged as shown in Fig. 2.2, where  $J_X=(x_{I-1}\dots x_1x_0)$  and  $P_X=(s_{K-1}\dots s_1s_0)$ .

#### 3. SELF-CHECKING CIRCUITS

Any digital system is exposed to internal failures which occur during normal functioning in its elementary modules and thus may produce incorrect results. Any logic circuit which is part of such a system can generate incorrect outputs due to two major causes: its internal faults and/or input errors generated by some other circuit in a system that feeds a given one. We have already seen that encoding inputs and outputs of a circuit (and internal states—if it is sequential) with some EDCs  $C_{IN}$  and  $C_{OUT}$  is a necessary means to implement it as SC. In this section we shall present various classes of SC circuits, depending on the degree of protection they offer against the most likely internal faults and input errors.

Prior to analysing the correctness of the output generated by a digital circuit with internal faults or input errors, we introduce the following notation. (This notation and concepts applies to a functional circuit and a checker as well.)

H — a combinational circuit

X — an input space of H (the set of all  $2^n$  input binary n-tuples);

Z — an output space of H (the set of all  $2^s$  output binary s-tuples);

$C_{IN}$  — an input code space of H,  $C_{IN} \subset X$ ;

$C_{OUT}$  — an output code space of  $\mathbf{H}, C_{OUT} \subset \mathbf{Z}$ ;

$X = (x_{n-1} \cdots x_1 x_0)$  — input vector of **H**;  $x_{n-1}$  and  $x_0$  are the MSB and the LSB, respectively;

$Z = (z_{s-1} \cdots z_1 z_0)$  — output vector of **H**;

X, Z — an input and output vector, respectively;

Xe — an input non-codeword;

F — the set of likely faults in H;

f — a fault in  $\mathbf{H}$ ;

Z = H(X) — a formal notation for: **H** maps input X to output Z when no fault is present in **H**;

Z = H(X, f) — a formal notation for: **H** maps input X to output Z when a fault f is present in **H**.

#### 3.1. Self-Checking Circuits with Internal Faults

A circuit **H** with an internal fault f can generate three types of output:

- 1. H(X, f) = H(X)—a correct output is generated for X despite a fault f; we say that the fault f is masked for an input X.

- 2.  $H(X, f) \neq H(X)$  and  $H(X, f) \notin C_{OUT}$ —an incorrect detectable output (a non-codeword output) is generated for X as a result of f; we say that the fault f is detected by X.

- 3.  $H(X, f) \neq H(X)$  and  $H(X, f) \in C_{OUT}$ —an incorrect output codeword is generated for X as a result of f; we say that the fault f causes undetectable output error, in a sense that an error cannot be detected just by observing whether H(X, f) is in  $C_{OUT}$  or not, which is the case in most SC circuits.

Apparently, the circuit  $\mathbf{H}$  achieves the TSC goal when only the first two cases occur, for every fault from some well-defined set of likely faults F. The most often it is assumed that F is a set of all single s/z faults,  $z \in \{0,1\}$ . However, there are several special classes of SC circuits which allow for extension of F with various classes of multiple faults (provided that a faulty circuit remains combinational). For instance, F can include: (i) any multiple fault in a single slice of a bit-sliced circuit protected by parity, (ii) any multiple unidirectional fault in an IF circuit using unordered code, (iii) any multiple fault in a circuit that is tested exhaustively during normal functioning. In this monograph, any possibility of extending F to include certain multiple faults will be mentioned, whenever applicable.

The class of circuits that achieve the TSC goal is formally defined in the following way.

**Definition 3.1.** [2] A circuit **H** is fault-secure (FS) for a set of faults F, if for every fault f in F, it never produces an incorrect codeword at the output for a codeword at the input, i.e.

$$(\forall f \in F) (\forall X \in C_{IN}) (H(X, f) = H(X)) \text{ or } (H(X, f) \notin C_{OUT}).$$

However, the FS property guarantees only that  $\mathbf{H}$  does not generate incorrect outputs for faults from F. Hence, another additional property is needed to guarantee that faults from F do not gather undetected inside a circuit  $\mathbf{H}$ , so that  $\mathbf{H}$  may loose its FS property due to undetected multiple faults (which are not in F anymore).

**Definition 3.2.** [20] A circuit H is self-testing (ST) for a set of faults F, if for every fault f in F, it produces a non-code space output for at least one code space input, i.e.

$$(\forall f \in F) (\exists X \in C_{IN} \mid H(X, f) \notin C_{OUT}).$$

**Definition 3.3.** [2] A circuit H is totally self-checking (TSC) for a set of faults F, if it is both FS and ST for F.

A functional circuit that is TSC for F guarantees its correct operation in the presence of internal faults, provided that each fault f is detected before another fault occurs. Designing TSC functional circuits is desirable, since the TSC property is very strong. Unfortunately, this property can be very difficult to achieve (if at all) in practical circuits and also a TSC realization of a functional circuit may be very costly compared to its non-TSC realization. The survey of design methods of TSC functional circuits using various EDCs can be found e.g. in [145], [159], [207]. To ease the design requirements, the following class of SC functional circuits was introduced, which achieve the TSC goal despite certain undetected internal faults.

**Definition 3.4.** [188] A circuit H is strongly fault-secure (SFS) for a set of faults F, if for every fault f in F, it is either TSC or it preserves the FS property while f is present.

The SFS circuits are the largest class of functional circuits with internal faults that meet the TSC goal. However, any SFS circuit can be converted into a TSC circuit by removing redundant gates or lines. Hence, the TSC functional circuits are a class of SC circuits which is most frequently considered in the literature however. Moreover, they are better suited for a formal rigorous verification of their FS and ST properties than all other SC circuits.

The construction of complex TSC systems, built using TSC modules as in Fig. 1.1, was considered in [111], [117], [187], and [207]. These works present some important general theoretical results regarding the *proper* and *optimal* placement of the checkers in a complex SC digital system, which guarantee that the TSC goal is achieved on a system level in the most efficient way. Of particular concern is

that all the error signals generated by the STCs are properly handled to monitor the correctness of the system operation [117]. Several implementations of complex SC modules and systems, using a variety of EDCs in each system, have been studied in [25], [37], [111], [121], [132], [169], [184], [207], and [213].

## 3.2. Self-Checking Circuits with Input Errors

Denote by  $X^e$  an input non-codeword resulting from errors in an input codeword X. The circuit H with an input error  $X^e$  can react in three different ways:

- 1.  $H(X^e) = H(X)$ —a correct output is generated for  $X^e$  despite input errors; we say that the *circuit* **H** masks an input error (or an input error is corrected by **H**).

- 2.  $H(X^e) \neq H(X)$  and  $H(X^e) \notin C_{OUT}$ —an incorrect detectable output (a non-codeword) is generated for  $X^e$ ; we say that an *input error*  $X^e$  is detected (propagated) by  $\mathbf{H}$ .

- 3.  $H(X^e) \neq H(X)$  and  $H(X^e) \in C_{OUT}$ —an incorrect undetectable output (an incorrect output codeword) is generated for  $X^e$  (or  $X^e$  causes an undetectable output error).

The qualification of the correct/incorrect behavior of the circuit  $\mathbf{H}$  with input errors depends on the function performed by  $\mathbf{H}$ . If  $\mathbf{H}$  is a functional circuit, the first two cases are acceptable since no undetected output error is produced in either case. However, if  $\mathbf{H}$  is a *checker*, i.e.  $\mathbf{H}$  is used to signal the errors generated by a functional circuit, then only the case 2) is acceptable, since  $\mathbf{H}$  should signal every occurrence of a non-codeword on its input. Otherwise (case 1), latent permanent faults may accumulate inside the system and deny its SC behavior for some faults from F. When an input non-codeword occurs, then a checker should signal its occurrence by generating a non-codeword output, although it is immaterial which of the error signals is actually generated. Also, when a checker is faulty and a given non-codeword cannot produce a non-codeword output (due to a fault), then it is immaterial what output codeword is produced (i.e. correct or not). This is the reason why the FS property, which is a must in TSC functional circuits, is not required for checkers.

Similarly as for internal faults, depending on how a circuit behaves in the presence of input errors, the following classes of circuits were defined.

**Definition 3.5.** [2] A circuit H is code-disjoint (CD) if it maps codewords at the inputs to codewords at the outputs and non-codewords at the inputs to non-

codewords at the outputs, i.e.

$$(\forall X \in C_{IN})(H(X) \in C_{OUT})$$

and  $(\forall X^e \notin C_{IN})(H(X^e) \notin C_{OUT})$ .

Let  $E_{IN}$  denote the set of non-codewords which can occur on the inputs of **H** as the result of the most likely faults in the circuitry that feeds **H**.

**Definition 3.6.** [111] The circuit **H** is error-propagating (EP) for  $E_{IN}$  if it is CD with input non-codewords limited to  $E_{IN}$  only.